Contents

On-demand webinar

How Good is My Shield? An Introduction to Transfer Impedance and Shielding Effectiveness

by Karen Burnham

Microvia failure occurs due to the thermal stresses that arise during the PCB assembly process. These stresses can have a significant impact on the reliability of the plated hole.

Key design strategies for enhancing microvia reliability include selecting suitable materials for laser drilling, adhering to IPC-T-50M guidelines, and implementing stack-up configurations in alignment with IPC-2226 standards.

Highlights:

- Factors contributing to microvia failures include the use of high-temperature dielectric materials and expansion rate mismatch during reflow.

- IPC-TM-650 2.6.27 and 2.6.7.2 methods offer comprehensive microvia testing procedures.

- The change in microvia resistance during the reflow cycle should not exceed 5% of the initial value.

3 primary factors that contribute to microvia failure

1. Usage of high-temperature dielectric materials

The transition to using high-tin alloys from tin-lead solders has led to higher working temperatures. This poses risks to copper interconnections and base materials during the reflow process, and microvias get damaged during the PCB assembly process.

2. Expansion rate mismatch

The discrepancy between the expansion rates of glass epoxy and copper during the reflow process, with glass expanding 200 parts per million and copper expanding 16 parts per million, results in connection failure in the microvia.

3. Multiple lamination cycles

HDI circuit boards may undergo multiple PCB lamination cycles and potentially affect the durability of the plated holes. This is due to continuous exposure to the high temperature and pressure during the lamination process.

To learn how to design a cost-efficient HDI PCB, download our design guide.

HDI PCB Design Guide

5 Chapters - 52 Pages - 60 Minute ReadWhat's Inside:

- Planning your stack-up and microvia structure

- Choosing the right materials

- Signal integrity and controlled impedance in HDI

- Manufacturing considerations for higher yields

Download Now

What leads to microvia failure during the reflow process?

Microvia failures typically occur at the interfaces with the capture pad and target pad.

Commonly observed microvia flaws include:

- Barrel cracks

- Corner crack between the capture pad and the target pad

- Target pad pull-out

- Misregistration of the ablated hole to the target pad

- Misregistration of the ablated hole to the capture pad

- Copper void in filled microvia

When the board undergoes thermal excursions during the reflow process, there will be an expansion in the z-axis. Due to the dissimilar CTEs of copper and the dielectric material, they expand at different rates. This causes separation at the microvia interfaces. This dislocation may not result in an immediate failure but could become latent.

These microvias open up when the temperature rises above Tg and close or self-heal when the temperature gets below Tg. Since these separations or cracks self-heal, the only way to identify them is to monitor the resistance of the microvia through the entire temperature cycle to observe that failure mechanism. IPC-TM-650 2.6.27 method helps manufacturers carry out microvia reliability testing using D-Coupons. We will discuss more about D-coupons in an upcoming section.

To know more about via protection method via tenting, read PCB via tenting design rules and fabrication notes.

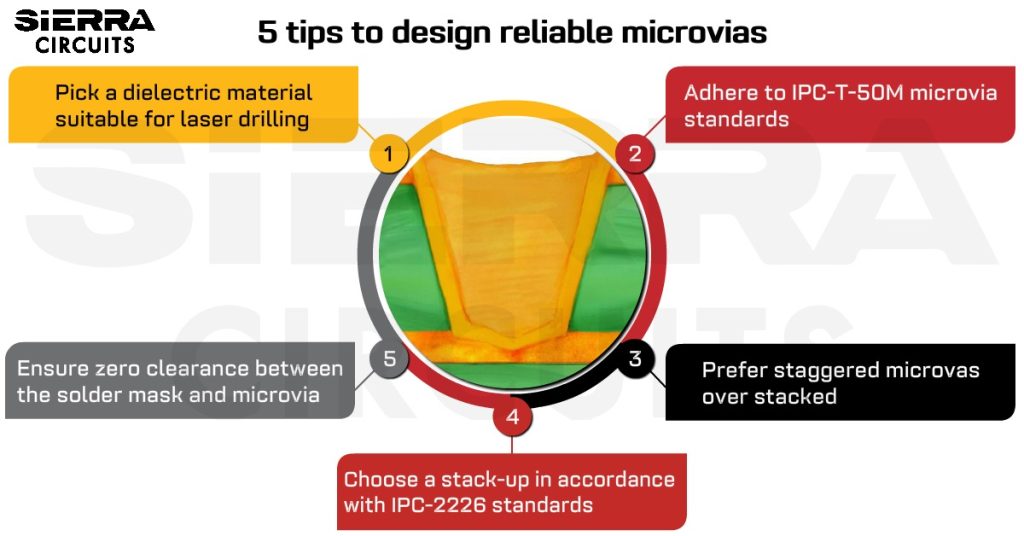

5 tips to design reliable microvias

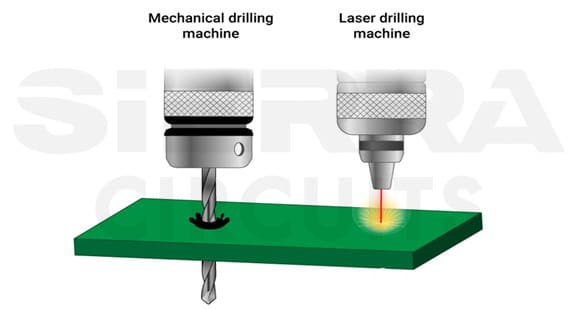

1. Pick a dielectric material suitable for laser drilling

Laser drilling offers controlled depth drilling and results in V-shaped drilled holes. This eases the plating process. For an efficient laser drilling process, maintain as much homogeneity as possible in your stack-up to avoid uneven heating and material inconsistencies. As a designer, you need to ensure the dielectric materials are laser drillable.

Isola FR408HR, FR370HR, I-speed, and Nelco N7000-2HT are a few examples of laser drillable dielectric materials.

Check out Sierra Circuits’ Material Selector for more such application-specific materials.

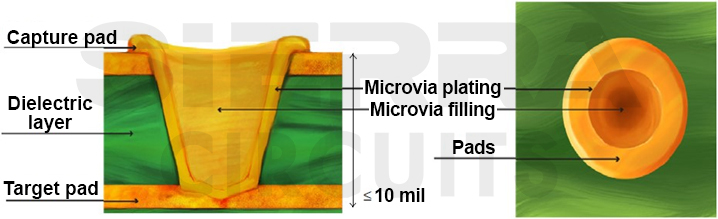

2. Adhere to IPC-T-50M microvia standards

The IPC-T-50M standards include:

- Maximum aspect ratio: 1:1

- Maximum diameter: 6 mil

- Maximum distance between capture pad and target pad: 10 mil

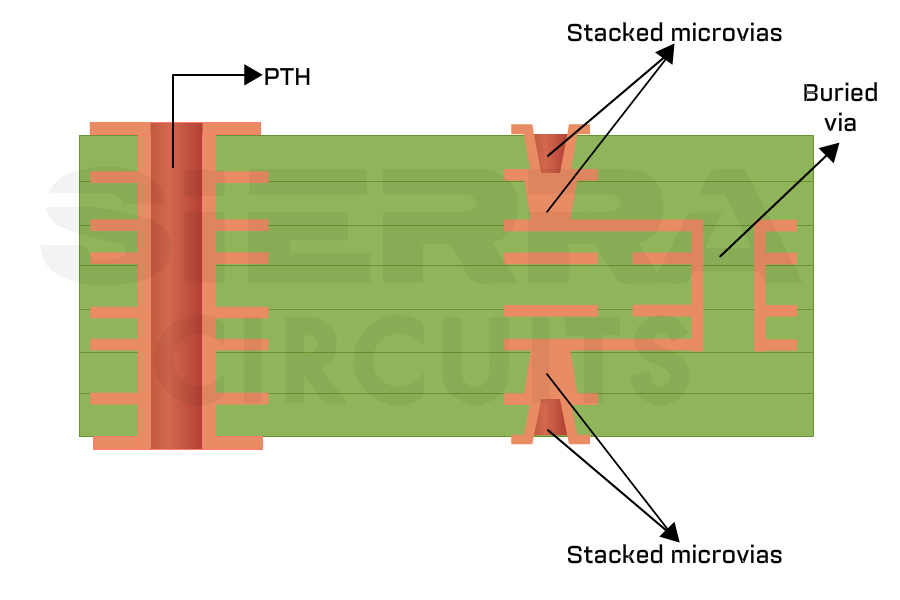

3. Prefer staggered microvias over stacked

Staggered plated holes can withstand multiple thermal cycles. This makes it more reliable when compared to stacked microvias. When you’re staggering the microvias, ensure the vertical separation between the centers of two microvias must be greater than the hole diameter.

To learn more about stacked and staggered microvias, see design and manufacture of staggered and stacked vias in PCBs.

We recommend a minimum of 2 mil spacing. For staggered microvias, only fill the vias on the external layers to reduce the overall cost of your board.

4. Choose a stack-up in accordance with IPC 2226 standards

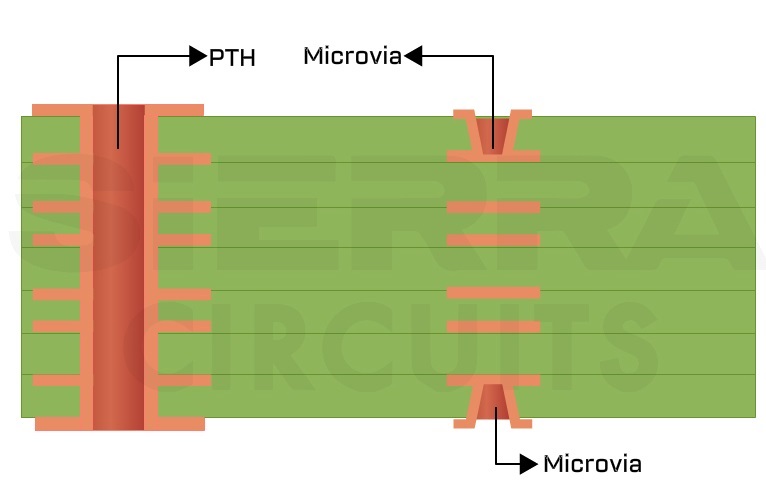

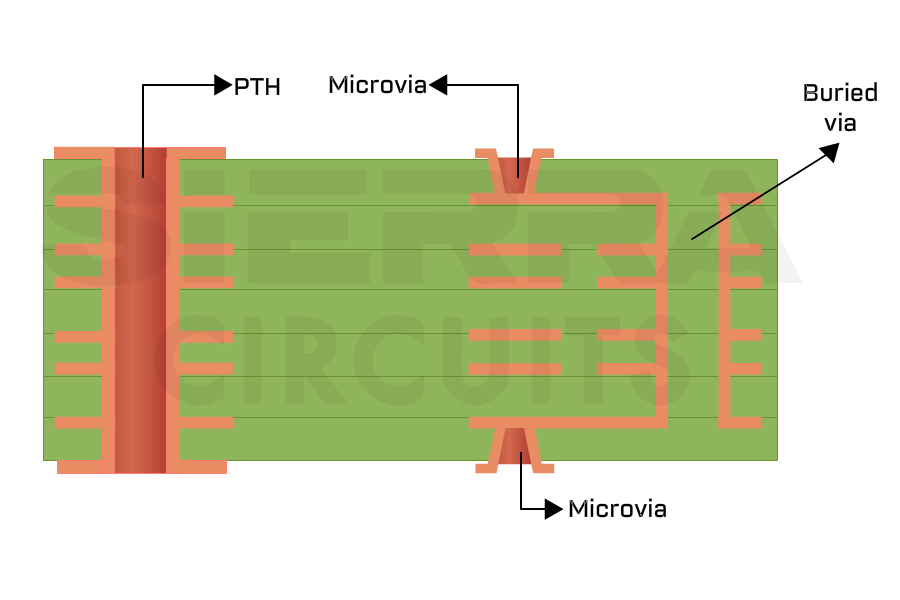

Choose a circuit board stack-up in accordance with IPC-2226 standards to ensure the manufacturability of your microvias and cost-efficient production. The images below depict the stack-up structures conforming to IPC-2226 standards. These structures ensure efficient heat dissipation and prevent thermal stress on the microvias.

IPC-2226 type I

This configuration features a PTH and a single microvia layer on either one or both sides of the core.

IPC-2226 type II

It has a PTH, buried via, and one microvia layer on one or both sides of the core.

IPC-2226 type III with stacked microvias

Type III configuration has a PTH buried via and at least two layers of microvias on either one or both sides of the core.

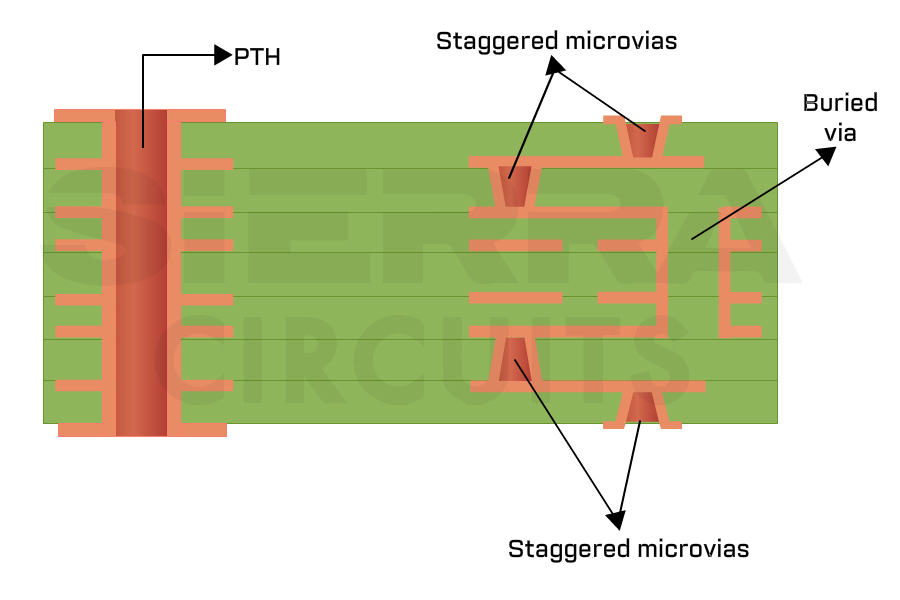

IPC-2226, type III with staggered microvias

Features a PTH, buried via, and at least two microvia layers on at least one side of a core with staggered microvias.

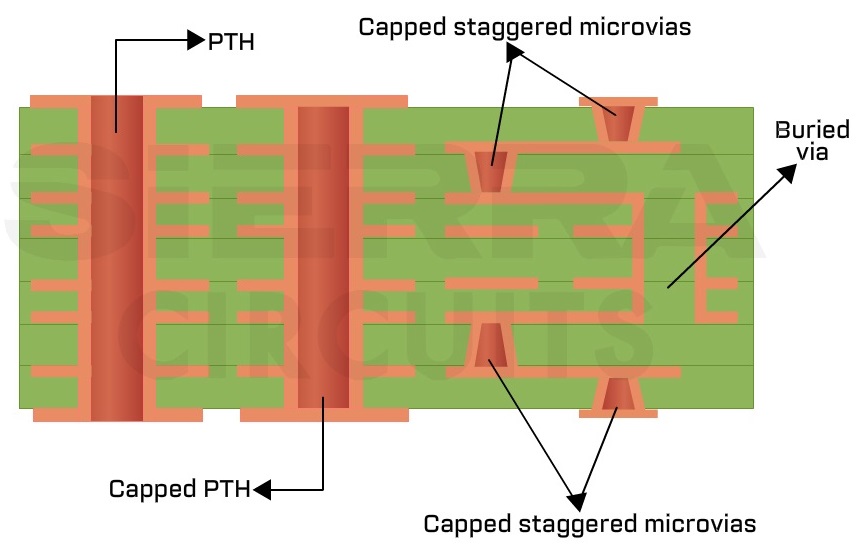

IPC-2226, type III, with filled, capped, and staggered microvias

This configuration features 2 PTHs with one of the holes capped. It has a buried via with capped staggered microvias on the outer layers.

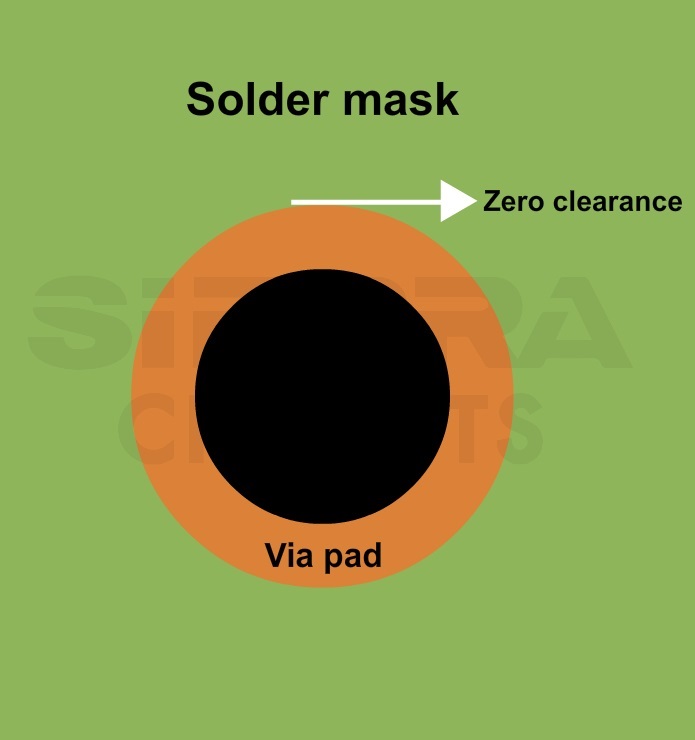

5. Ensure zero clearance between the solder mask and microvia

When there’s a gap between the solder mask and microvia, the risk of solder bridging increases during the reflow process. The solder can flow into the gap, creating an undesired connection between adjacent traces. This is one of the important DFM guidelines you need to follow.

For more DFM standards, download our design guide.

Design for Manufacturing Handbook

10 Chapters - 40 Pages - 45 Minute ReadWhat's Inside:

- Annular rings: avoid drill breakouts

- Vias: optimize your design

- Trace width and space: follow the best practices

- Solder mask and silkscreen: get the must-knows

Download Now

Designing test coupons for testing microvia reliability

Test coupons are small PCB sections (typically 200x30mm). They are designed and manufactured alongside the main circuit board, with identical configurations. These coupons are used to assess the quality and reliability of class 3 PCBs.

You can place these coupons either in a separate section on the same panel, integrate them within the main PCB layout, or design them separately based on your requirements. Test coupons enable you to subject them to a spectrum of tests, encompassing reflow simulations and thermal shock assessments.

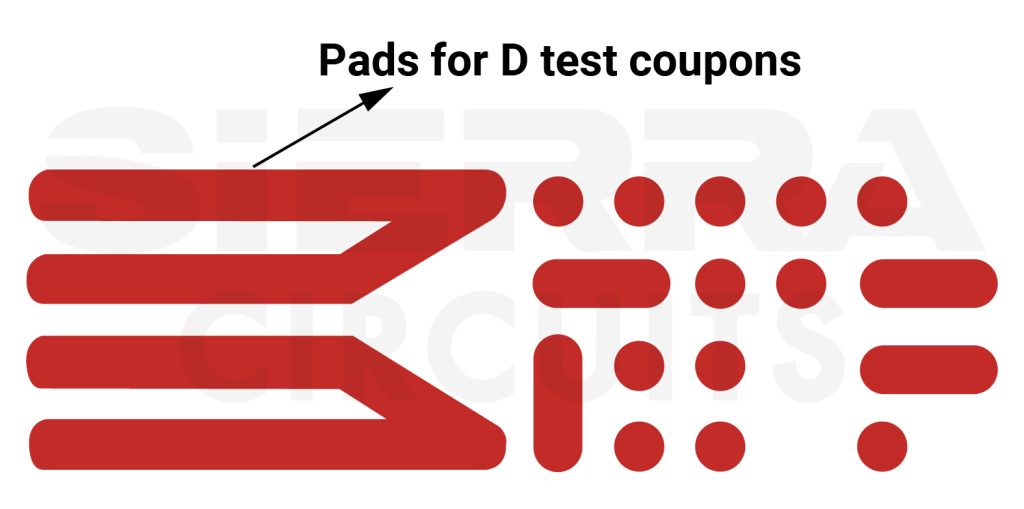

For plated holes and via thermal stress testing, we use D coupons. You need to design these coupons in accordance with IPC-2221 Appendix A or B. D coupons enable you to contain enough plated holes or vias in a chain to achieve a precise resistance measurement. As a result, these D coupons are suitable to carry out microvia reliability testing for all the different testing methods such as HATS 2.6.7A, current induced thermal cycling test, micro-etch evaluation, and IPC-TM-650, Method 2.6.27.

D coupons feature two nets representing the holes and via structures associated with components. Furthermore, D coupons can be designed with A and B features or propagated structures such as blind vias, buried vias, or filled-through holes. The D-coupons are suitable for microvia reliability testing as they represent diverse propagated via structures and transitions found in actual circuit boards.

Fab notes for microvia reliability testing

Include these points in your fab notes if you wish to test the durability of the microvias present in your design:

- The purpose of the D-coupons is to test the reliability of plated holes.

- Hole sizes, plating requirements, and spacing between the copper features.

- Number of test coupons and the desired location on the PCB panel.

IPC-TM-650 test methods for microvia reliability

IPC, in collaboration with various OEMs and the D-32 Thermal Stress Test Methodology Subcommittee, has introduced a test method for assessing the reliability of electrical interconnections. They include:

- IPC-TM-650, method 2.6.27

- IPC-TM-650, method 2.6.7.2

These methods involve measuring the electrical resistance of test coupons at different temperatures. In method 2.6.27, the procedure involves subjecting the test coupon to a standard solder paste reflow profile designed to achieve a peak temperature of either 230°C or 260°C.

The system monitors the resistance of the coupon as you run it through the thermal cycle. The D coupon remains connected to a 4-wire resistance measuring unit throughout this process. The connection is maintained for a total of six full reflow profiles. In method 2.6.7.2, D coupons are subjected to a minimum of 6 reflow simulations and 100 thermal shocks from -55°C to 210°C.

The resistance should not increase by more than 5% during this testing phase. If this is not achieved, the device under test is considered failed.

During the reflow simulation, resistance measurements will be monitored at least every second and once every cycle during thermal shock. By implementing this testing technique, OEMs have the ability to identify and address latent microvia failures. This helps safeguard their products against potential defects that may go unnoticed.

Key takeaways:

- Microvia failures typically occur at the interfaces between the target and capture pads.

- Adherence to IPC-T-50M microvia standards is crucial to designing a reliable microvia.

- Prefer staggered microvias over stacked ones for better reliability during thermal cycles.

- D coupons are used for microvia reliability testing.

- Continuous resistance monitoring during reflow is essential for identifying latent microvia failures.

Appropriate material selection, adherence to IPC-T-50M guidelines, and stack-up configurations as per IPC-2226 standards play pivotal roles in enhancing microvia reliability. Continuous monitoring of microvia resistance during reflow, with a threshold of 5% change, is essential. Implement these design techniques in your next design to ensure durable microvias.

Need design assistance to design reliable microvias in your PCBs? Post your queries on SierraConnect. Our design and manufacturing experts will answer your quires.

How does the choice of dielectric material impact the efficiency of laser drilling in PCB design, and what considerations should designers keep in mind for optimal results?

In microvia design, what advantages do staggered configurations offer over stacked ones, and how can we enhance the reliability of PCBs during thermal cycles?

The dielectric material significantly influences laser drilling efficiency. Optimal results are achieved by selecting materials like Isola FR408HR, FR370HR, I-speed, or Nelco N7000-2HT, known for being laser drillable. You should ensure material homogeneity in the stack-up to prevent uneven heating and inconsistencies, ultimately facilitating controlled-depth laser drilling.

Staggered microvias outperform stacked counterparts in withstanding thermal cycles. Their strategic arrangement ensures greater reliability by minimizing the impact of thermal expansion. Designers should maintain a minimum 2 mil spacing, predominantly fill external layer vias for cost efficiency, and ensure vertical separation between centers greater than the hole diameter for optimal results.