Contents

On-demand webinar

How Good is My Shield? An Introduction to Transfer Impedance and Shielding Effectiveness

by Karen Burnham

Decoupling is a way of isolating signal components from composite signals based on frequency. Therefore, understanding which range of frequencies should be isolated is important for accurate decoupling capacitor placement in a system.

In this article, you will learn important decoupling capacitor placement strategies to have an efficient power distribution network (PDN) and I/O signals.

The separation of AC and DC signals is vital for PCB assemblies or else it will impact both signal integrity and power integrity. Poor decoupling also results in power bus noise, leads to EMC issues, and affects product reliability.

Decoupling capacitors are used for power supply and transient decoupling because of their intrinsic energy storage capability. Complex PCB assemblies have multiple power supplies that require voltage regulation to ensure the proper operation of components such as processors, FPGAs, ICs, or amplifiers.

These capacitors supply current to maintain the voltage levels of the components when needed. Effective decoupling depends upon the capacitor type and its placement on the board.

Concept of PCB decoupling

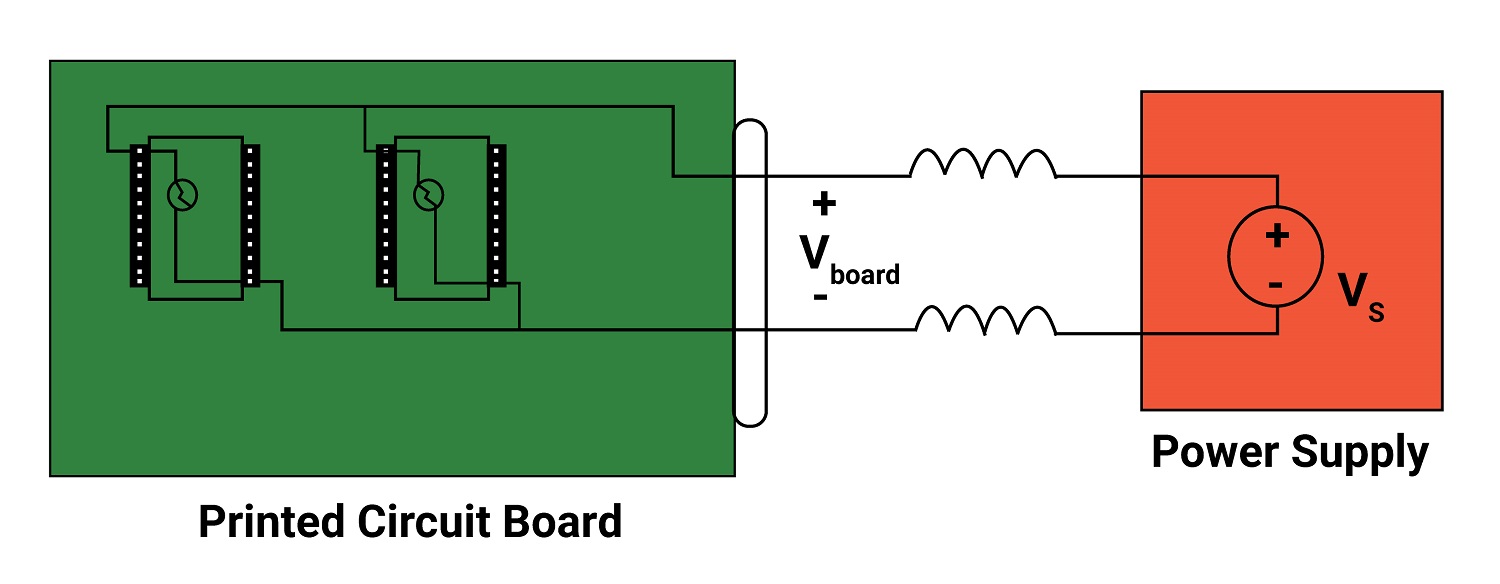

When an active device on a PCB shows a sudden change in the amount of current it draws, it causes a drop in the supply voltage across the connection trace impedance. This voltage drop impacts the functioning of all the devices on the board, not just the switching device.

If the voltage drop is too high, the circuits on the PCB may fail to operate properly. The voltage fluctuations on the power bus generate conducted or radiated electromagnetic interference (EMI) problems.

The voltage fluctuation can be controlled by placing a capacitor between the power and ground conductors near the active devices. This capacitor acts as a local charge reservoir that controls sudden changes in the current while balancing the voltage on the power bus.

Power bus decoupling capacitor placement strategies

PCBs can be segregated into three categories for power bus decoupling:

- Boards that do not have power planes

- Boards with closely spaced power planes

- Boards with broadly spaced power planes

Boards that do not have power planes

Decoupling capacitor placement is easier for boards that do not have a power plane. This is significantly true if the PCB has one or more solid ground planes. When power is distributed on traces, designers find it challenging to control the power bus noise seen by each device.

The optimum isolation between the active devices on the board allows the designer to decouple each device individually. It ensures that the device’s high-frequency current requests are fulfilled without permitting unacceptable voltage swings at the power input pins.

Here are some guidelines for decoupling capacitor placement on PCBs that do not have power planes:

- Place at least one local decoupling capacitor for each active device on the board.

- Place at least one bulk decoupling capacitor for each voltage distribution on the board.

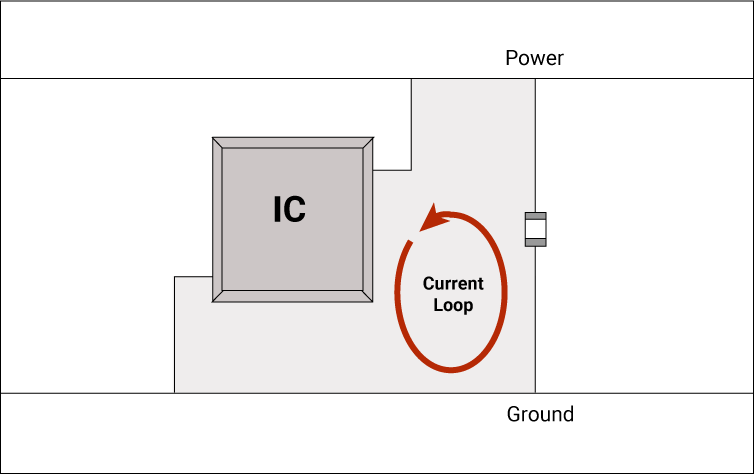

- Connect local decoupling capacitors between the voltage and ground pins of the active device. Make sure that the area of the loop formed by the capacitor connection is minimal.

- Place bulk decoupling capacitors near the entry point where a voltage enters into the board. If the voltage is generated on the board, then these capacitors should be planted close to the location where it is generated.

- The size of the bulk decoupling capacitors is chosen according to the momentary (transient) current requirements of the entire circuit board. Placing two local decoupling capacitors having the same nominal value is better than placing one capacitor having twice the nominal value. The reason is two capacitors have a lower overall connection inductance and provide better high-frequency filtering to the rest of the power bus.

Boards with closely spaced power planes

Placing decoupling capacitors on a PCB having closely spaced power planes requires a different approach. It is because the planes contribute a decoupling capacitance (due to their close proximity) that becomes significant at high frequencies.

- Choose the largest nominal capacitance available. Do not use capacitors with a theoretical capacitance less than the parallel plate capacitance that naturally exists between the power and power-return planes. A PCB made with FR-4 material containing one pair of power distribution planes spaced 0.25 mm (10 mils) has an inter-plane capacitance of approximately 16 pF/cm2.

- The local decoupling capacitors’ placement is not critical because their performance is influenced by the connection inductance associated with planes. They can be located anywhere within the vicinity of the active devices based on their effective operating frequency.

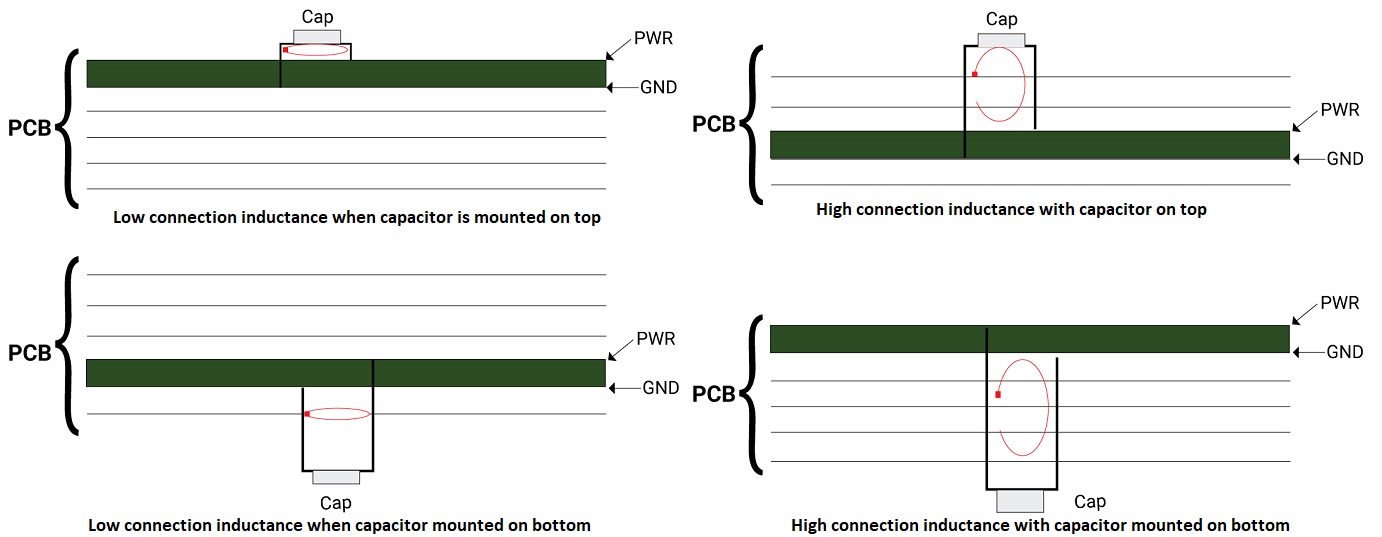

- The number of decoupling capacitors is roughly inversely proportional to the effective connection inductance. That is why high-speed circuit boards often have many local decoupling capacitors for every active device. Connection inductance is calculated by the loop area formed by the capacitor body, mounting pads, traces, and vias.

- Refrain from using traces attached to a decoupling capacitor pad. Place vias within or near the pad, preferably as close as possible.

- If there is no scope for locating the via adjacent to the capacitor pad, then move the entire capacitor. Actually, capacitor location doesn’t matter, but connection inductance is crucial.

- Mount all local decoupling capacitors on the board nearest to the planes. Connection inductance is approximately proportional to the distance from the planes.

Controlled Impedance Design Guide

6 Chapters - 56 Pages - 60 Minute ReadWhat's Inside:

- Understanding why controlled impedance is necessary

- Stack-up design guidelines

- How to design for impedance

- Common mistakes to avoid

Download Now

Boards with broadly spaced power planes

If the power and ground planes on a PCB are separated by at least 0.5 mm, then the inductance between the planes can’t be neglected. This rule is applicable to most 4-layer boards manufactured with 1 mm cores and multi-layer boards that have signal layers in between the power and ground layers.

- The total value of the bulk decoupling capacitor is evaluated by the transient power requirements of the active devices on the board.

- Local decoupling capacitors play a major role at higher frequencies. The inductance of their connection to the power distribution planes is far more critical than their nominal capacitance.

- Local decoupling capacitors should be put as near as possible to the power or ground pins of the active device they are decoupling. And the pin on which the capacitor should be located can be determined by identifying the farthest power distribution plane from the active device.

- Choose the largest nominal capacitance available. Nominal capacitance values are not as critical as connection inductance.

- Orient the local decoupling capacitor so that the pin connected to the most distant plane is nearest to the active device’s pin connecting to that plane.

- Locating the decoupling capacitor near to the active device to share the same via is an adequate choice. However, a trace should not be used between the capacitor mounting pads and the vias. To learn how to design efficient signal paths, read 10 best layout tips for high-speed and high-current PCB traces.

- Never use traces on decoupling capacitors to reduce the connection inductance. Locate the via adjacent to the mounting pad and the two capacitor vias as close together as possible. Also, mount all of the local caps on the board nearest to the planes.

Where should you place decoupling capacitors for signal and power integrity?

Mount the capacitor in parallel (for power pins and grounds)

Decoupling the I/O signal paths and power distribution and grounding is not that important, but the elimination of AC or coupling of DC is critical. Therefore, the capacitor should be connected in parallel with the signal path.

To minimize high-frequency EMI, connect a capacitor in parallel with a resistor

Decoupling capacitors can also be connected in parallel with resistors to filter out unwanted HF while allowing LF and DC to flow through.

Place the capacitor near the signal source

Decoupling capacitors should be placed as close as possible to the source for decoupling the signal. This means the caps should be placed on the pin for ICs and near the connector for I/O signals.

Connect capacitor in series for I/O signal traces

To remove low-frequency transients from input and output signals, the capacitor should be connected in series with the trace. High-frequency will pass through the capacitor, but low-frequency and DC will be blocked.

Additionally, small caps should be used for high-frequency transients and large caps for low-frequency transients.

Place the capacitor between digital and analog ground pours

Decoupling capacitors can also be used to separate analog and digital signals. In some cases, the same ground pour is used for analog and digital components. To avoid high-frequency noise being coupled from digital to ground, connect decoupling capacitors between them.

Connect the capacitor between the component’s power pin and via

Place the capacitor between the component’s power pin and the via that connects to the power plane. This ensures smooth current flow through the plane.

Daniel Beeker shared his insights, saying, “While placing the capacitor, employ the 20th wavelength of transistor switching speed. Implement the capacitor as near as possible to the IC pin to limit the propagation time.

When you consider one nanosecond switching event, place the capacitor at half an inch of distance for a good power supply within the 20th wavelength. Usually, capacitors are attached to the bottom side of the board for BGAs. For QFPs and similar packages, it is implemented across the pair of leads.”

Also, read 11 best high-speed PCB routing practices.

Decoupling capacitor placement guidelines for BGAs

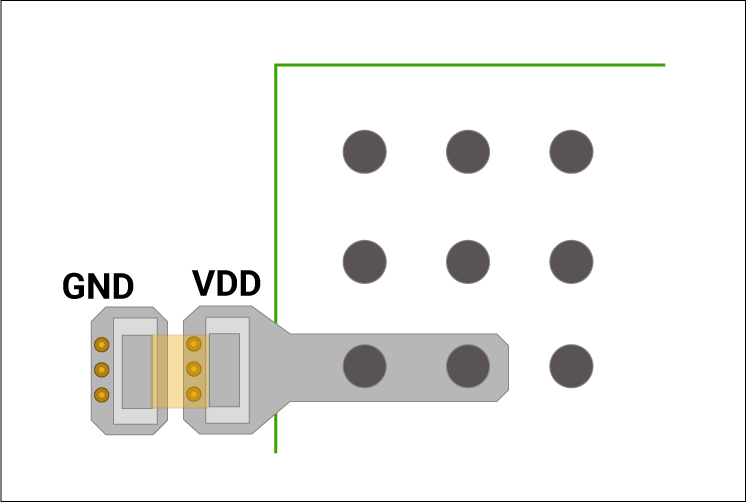

- Place decoupling capacitors on the opposite side of the BGA right under the pin itself.

This is how BGA will be fanned out with a via that is on the pad. Later, it can be filled with a conductive or non-conductive filling.

- Instead of placing one via per ball inside the power/ground section of a BGA, skip every other row and share every via with two power or ground balls.

This will allow capacitors to fit directly underneath the part and minimize the inductance when compared to placing the capacitors outside the footprint area.

Note: It’s a good idea to limit the number of power balls shared with one via.

- Place the bypass capacitors on the opposite side of the board in the courtyard region for a perimeter matrix BGA. Orient the capacitors so that the BGA power pin fanout via can also serve as the capacitor’s connecting point. This provides the lowest inductance channel for power while allowing via space for signal routing.

When placing the bypass capacitors within the matrix, try to do so only when there are existing vias available as a part of the BGA fanout pattern.

Adding extra vias in these areas is possible. But be aware that extra vias will also reduce the copper channels on the internal power and ground planes due to the fanout pattern being in four directions.

- A solid BGA matrix has ground pins in the middle, surrounded by one or two rows of power pins. When this occurs, auto fanned-out vias of the outer row of ground pins can be removed and can be fanned back into the next inner row.

This method creates a channel around the middle block of ground pins by enabling bypass capacitors placement on the bottom side of the board. To achieve this, it may be required to reduce the size of some of the power capacitors. As a result, a large number of bypass capacitors are placed significantly closer to the power pins.

High-Speed PCB Design Guide

8 Chapters - 115 Pages - 150 Minute ReadWhat's Inside:

- Explanations of signal integrity issues

- Understanding transmission lines and controlled impedance

- Selection process of high-speed PCB materials

- High-speed layout guidelines

Download Now

Where should you place bypass capacitors?

The placement of capacitors is one of the most critical phases of the PCB design process. Incorrect capacitor placement can completely revoke their performance.

- Place capacitors on the bottom side of the board with respect to SMT component placement.

It is advisable to place SMT components on the bottom because capacitors are usually placed under the pads of SMT components. Placing them on the bottom side provides more space for fanout traces and vias. If you are placing capacitors on the top side, locate them as close as possible to the power pins of the components.

Learn how to place components in KiCad with our easy guide.

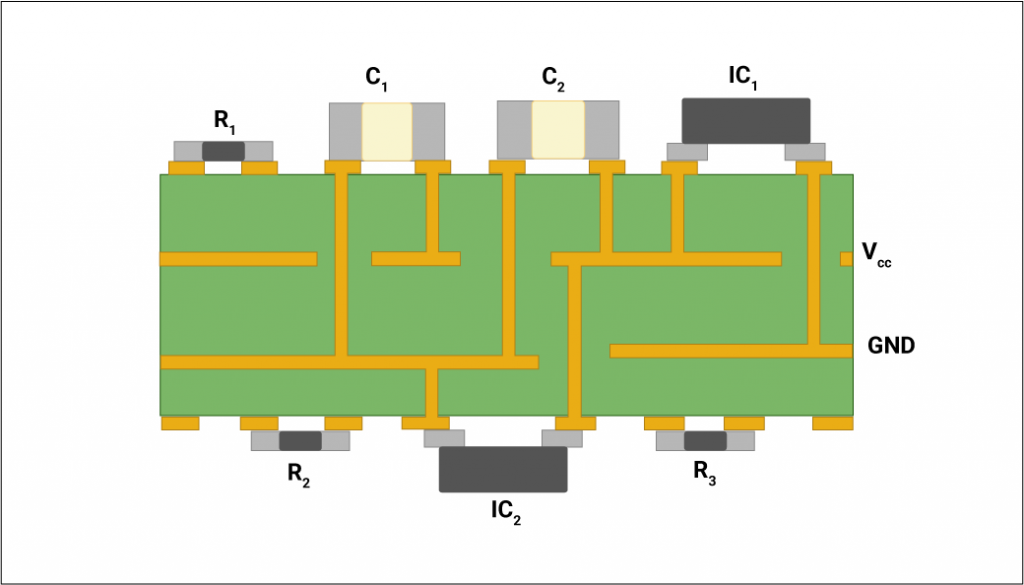

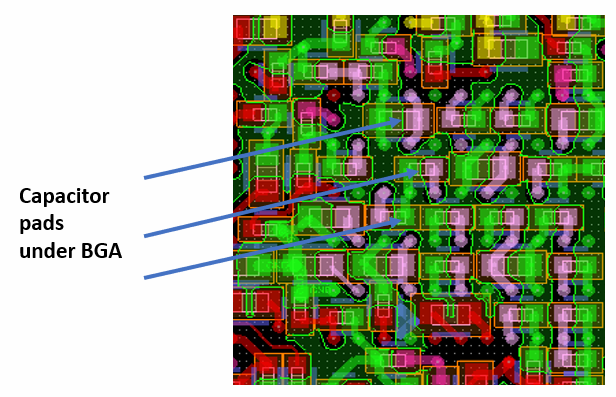

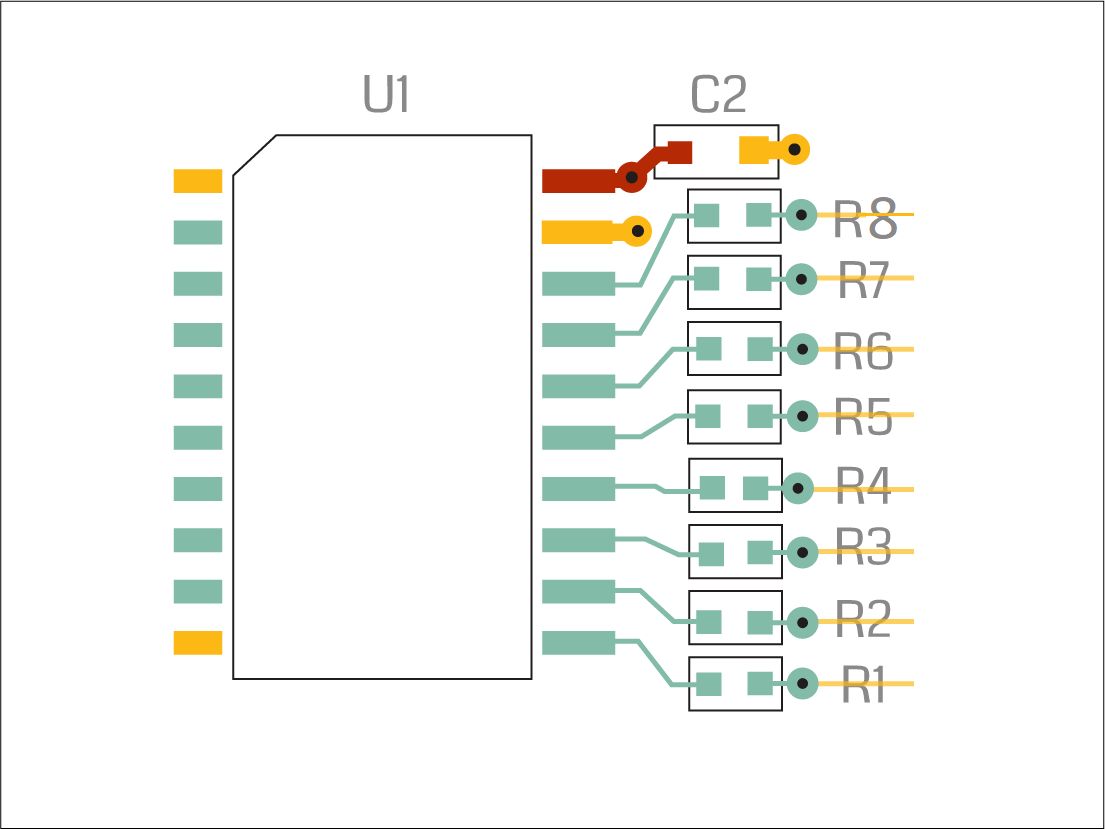

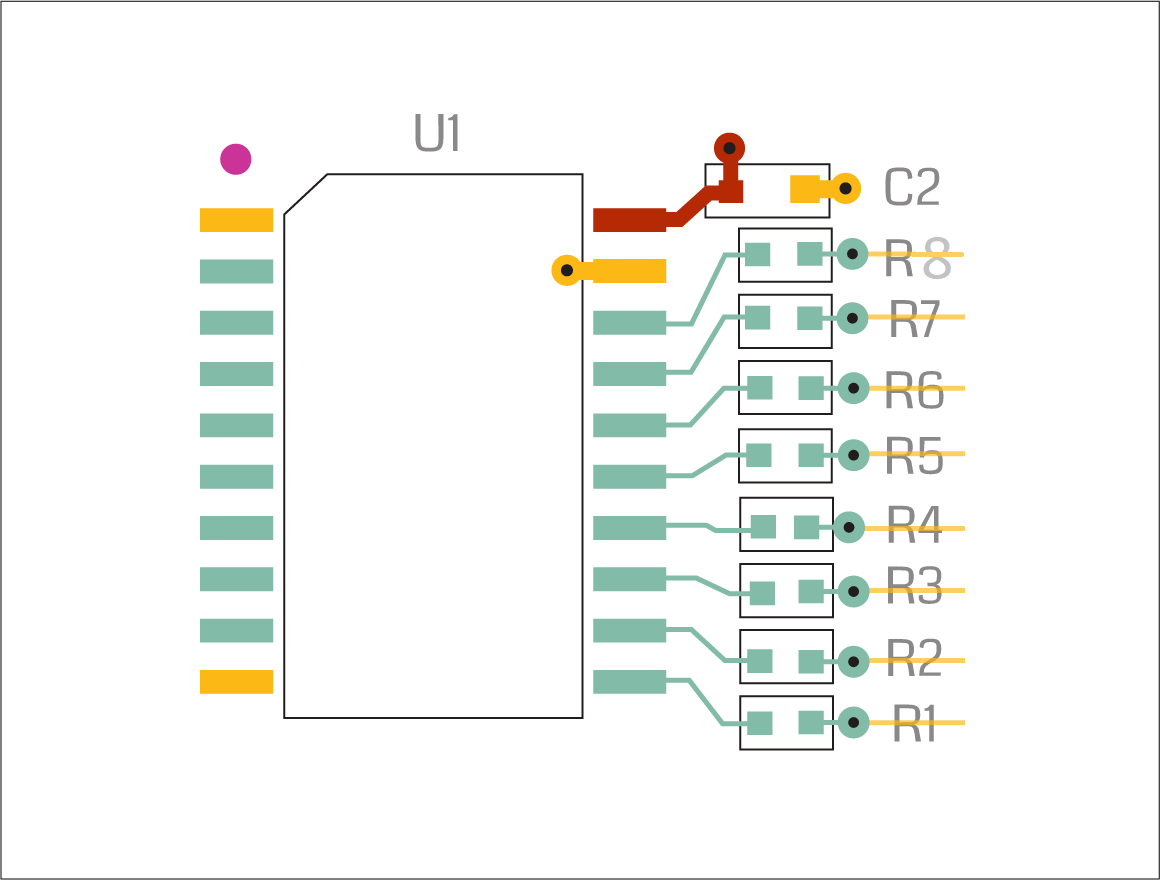

As shown in the above figure, the bypass capacitor takes up extra space on the top side and, hence, reduces the available space for vias. As shown in the figure given below, since the capacitor is placed on the opposite side, it can be placed underneath the pads of the IC on the top. So, there is no via space loss.

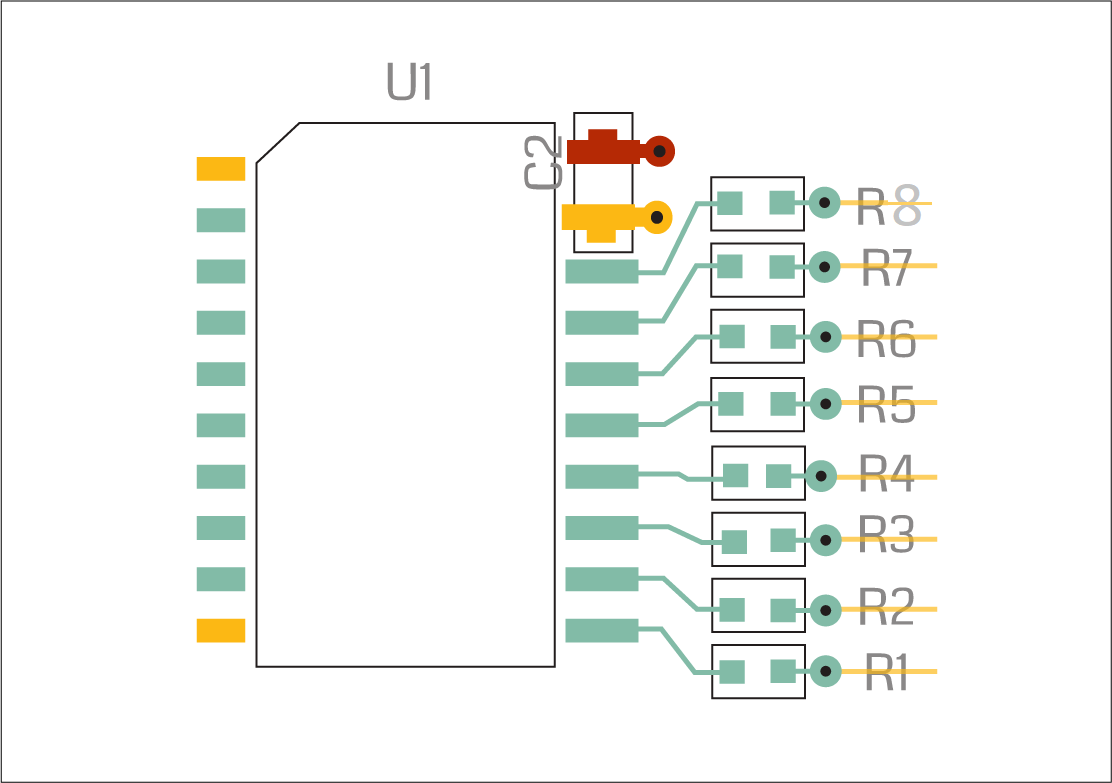

The method shown above is the preferred way among PCB engineers. It not only provides more via space but also has the advantage of keeping the ground path shorter by connecting the ground side of the capacitor directly to one of the device’s ground pins. This provides a shorter, less inductive ground system around the IC.

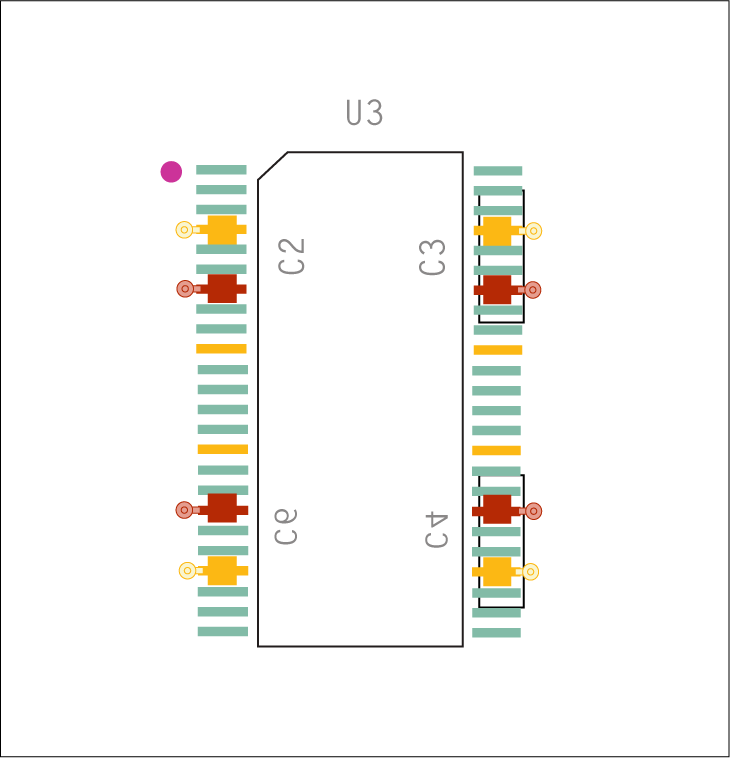

- When connecting multiple capacitors of different values to the same supply pin on an IC, place the lowest-value capacitor closer to the device pin.

The lowest value capacitor provides switching current for the maximum frequency supply current requirement. When the output of a digital device changes from an ‘OFF’ state to an ‘ON’ state and vice-versa, the current required to do this becomes quite high for a short period of time. Connecting low-value capacitors close to the pin enables the supply of small current rapidly to the switching device. This is due to the fact that these capacitors have a shorter time constant. The current requirement is reduced once the output returns to a steady condition.

If the only capacitors available to produce this near-instantaneous current are larger-value capacitors then the output will not be able to switch at the desired speed due to the longer time constant of capacitors. This can cause serious timing problems in the design.

Incorporate two local decoupling capacitors instead of one with double the value to improve capacitor filtering efficiency . Capacitors’ equivalent series inductances (ESL) and resistances (ESR) reduce when placed in parallel. When selecting the capacitors, you need to consider their specifications also. If the two capacitors have the same dielectric material, size, and voltage rating, their DC bias effect will be similar to that of a single capacitor with double the value. However, if they differ in specifications, their combined capacitance may not precisely match that of a single capacitor with double the value.

Atar Mittal, General Manager at Sierra Circuits, explains, “When you have multiple capacitors with different values and resonant frequencies in a circuit, there is a possibility of generating resonance peaks in the frequency response of the circuit. These peaks can lead to impedance discontinuities at specific frequencies. To avoid this, you can incorporate multiple capacitors of the same value near the power supply.”

When we interviewed power integrity expert, Steve Sandler, he said, “To calculate the exact capacitance needed, use the formula, C = L / (R²), where L is the inductance of the power plane, and R is the target impedance. The capacitor’s ESR should be close to the target impedance to maintain a flat impedance profile. However, it’s challenging to balance low inductance with the right ESR, and paralleling capacitors might lower ESR too much, causing new resonances.”

- Place larger non-polarized capacitors and tantalum capacitors near the pin or device in ascending order of capacitance value. Tantalum capacitors provide current faster than the system power supply. These capacitors recharge the high-frequency capacitors more quickly than the system supply can respond.

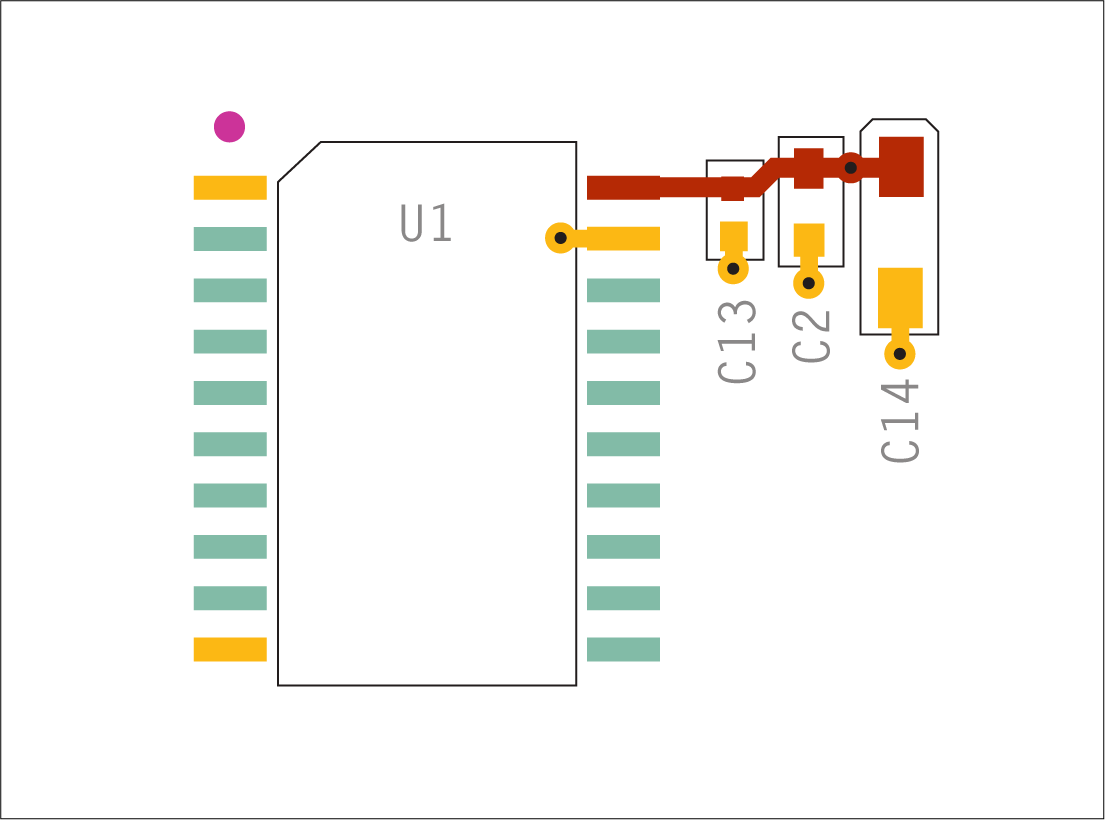

In the figure shown below, the capacitor with the lowest value (C13) is put closest to the device power pin, followed by C2, and C14. The tantalum can be placed above or below the device as long as it is close to U1 and will not affect the performance.

The space to the left and right of an IC is generally used for fanouts or other components that need attention before the tantalum. As the capacitance value increases, the number of capacitors of each value normally decreases.

There could be four to six ceramic capacitors for one tantalum capacitor. Capacitors larger than 10uF can normally be distributed across a larger region.

- Use at least one bypass capacitor per power pin for devices having multiple power pins.

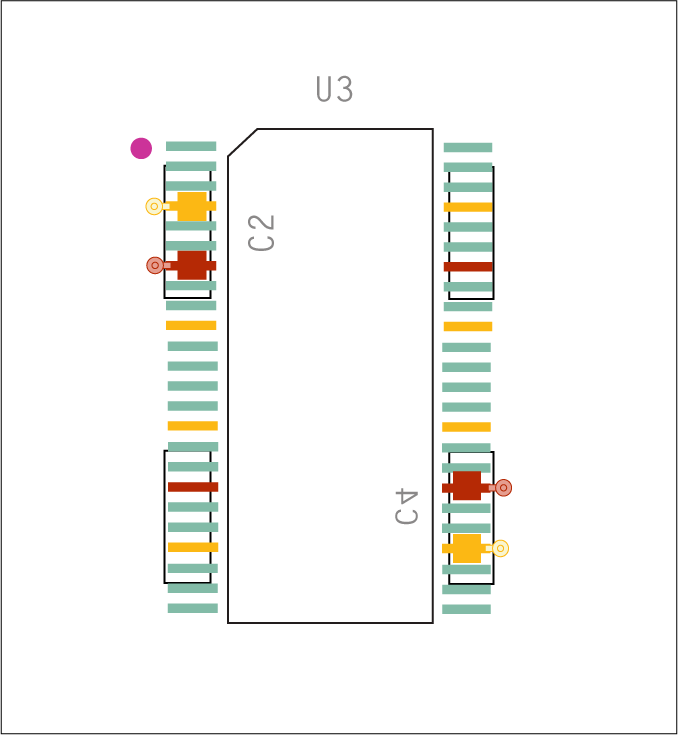

If the design only allows for two bypass capacitors, then place one on either side of the device.

To avoid ground bounce problems (because many outputs switch simultaneously), add two more capacitors per device, as shown below.

- Refer to the schematic to ensure the placement of bypass capacitors at the device power pins and not at high logic pins.

Capacitors are the most versatile components from the PCB assembly standpoint, and decoupling is one of their chief functions. In fact, the board’s signal and power integrity may potentially depend on how effectively decoupling capacitor placement is done.

To understand the basics of decoupling caps read, what is the use of a decoupling capacitor. Let us know in the comment section what you want us to write next in the decoupling capacitor series.

Have queries regarding decoupling capacitor placement? Post them on our forum, SierraConnect. Our design experts will resolve them.